#乌合麒麟收回道歉#技术问题就来讨论技术,首先呢,华为那个专利写的是一种跨芯片同步技术,这个技术不是用来跑性能的,大家疯狂热议的什么1+1大于2的本质上是认为两个芯片加起来能赶上一个芯片的性能。而这个专利是一个跨芯片的同步技术,比如解决一些共享资源的访问问题,两个芯片上的程序读写同一段内存数据,现在只有在操作系统软件层面设置信号量获得信号量的才能访问,这个性能很差,芯片支持的话会把系统调度级别的等待提高到芯片时钟级别,解决的是特定问题。

但要强调,不是靠这个提升性能!!!同步技术不论在什么层面上,本质上是把处理串行化,一个一个来处理。多核处理器性能的提升是要并行化,互相不影响,各干各的没有等待才是高性能。

所以,这个事件呢,是那个无知者无畏的起名华为影业的蹭华为热度的自媒体看到了个专利,也不知其所以然,然后自己脑补起来,煽动情绪,写了一大堆跟专利目的毫无关系的东西。

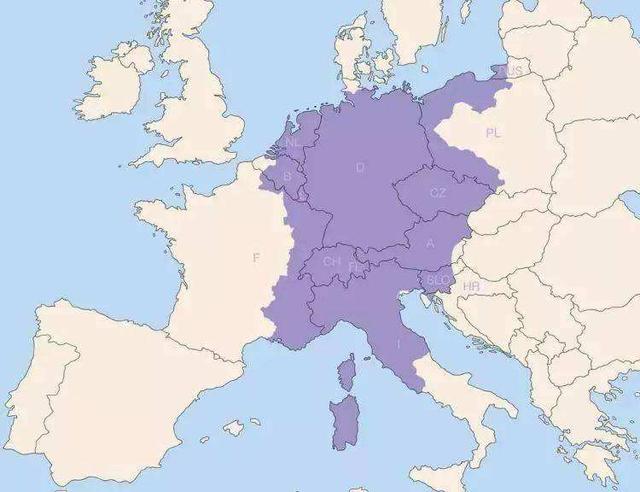

至于芯片封装技术,是可以用多个DIE搭建出一个大芯片,专业称之为chiplet,有兴趣的可以搜这个关键词。但一般用在两个场景:一是芯片太大了,一个die面积太大制作不出来,拆分一下放在两个die上,但die2die互联代价十分大,拆分出来的两个die从面积到功耗都要大于不拆分的(如果能做出来)。二是降低成本,典型的就是amd的cpu,芯片成本主要在投片,amd需要生产出来高中低各种档次的cpu应对市场,如果你为每个档次各投一次片,成本太高了,于是amd只投一次最基本的die,低端的封装一个die,中端封2个,高端封4个。但实际上amd还是为了多die的互联又投了个互联die。现在已经大规模用的封装技术是建一个基板由它对外出管脚,然后把多die放在这个基板上封装起来,属于2.5d。3d的把两个die摞起来的台积电有,但太贵了,还不成熟,没有大规模商用,amd最新的路标里面有这个东西。然后还有人提什么内存,flash的多层封装那跟处理器完全不是一个概念,这里不扯了。

最后,基本物理规律还是要遵循的,两个14nm芯片对等的是两个7nm芯片而不是一个,大家都封你说哪个厉害?实际上14nm跟7nm在面积上差距不止一倍,主频功耗还有30%的差距,也就是说你拿个100mm^2的14nm芯片,同样功能性能用7nm花40mm2就做出来了,主频还高30%。你怎么比?理论上两个这样的14nm芯片用7nm只需要花80mm2就做出来了,芯片间还是内部互联,主频高,功耗低一倍多。

请大家理性爱国,避免受那些蹭热点,恶意炒作,消费华为,造谣传谣甚至捧杀华为的人的影响。发这种文章的一定不是华为人,也不是华为授意的。

嵌入式开发门槛高,涉及的知识面广,既要求懂硬件,又必须能写软件,而软硬件涉及的知识体系却又是异常的庞大;并且学习这些短期内看不到成绩,需要坚持数年,执着在一个领域深耕。

具备基本的电路知识,了解常用元器件、芯片,能看懂原理图,作为嵌入式软件开发人员也必须懂一些硬件设计方面的知识;

具备一定的MCU设计与应用能力,从单片机到ARM再到DSP,能够根据客户要求设计产品;掌握至少一种单片机的编程与使用,比如常见的STM32,后期可以涉猎FPGA;

学习C语言,掌握基本的数据类型、指针、结构体等;了解基本的MCU外围模块,SPI、I2C、UART、GPIO、ADC、PWM、Timer、FLASH等原理,能根据硬件原理以及芯片手册编写裸机设备驱动程序;掌握常用工业通讯协议比如CAN、Modbus等;

学习至少一种操作系统,包括但不限于uCOS、FreeRTOS、RT-Thread、Vxworks等,并且一定要学习嵌入式linux的使用与编程,搞明白多任务调度、信号量、邮箱等的原理与使用;

学习linux平台下的设备驱动程序设计,掌握字符设备、块设备、网络设备的驱动框架,并能够熟练设计这些设备驱动,比如ADC、UART、SPI、GPIO、Camera等等,视频驱动框架一定要搞懂V4L2;

学习GUI设计,具备基本的嵌入式产品GUI设计能力,可以学习Qt,它的跨平台特性很适合嵌入式开发;当然也可以转到App设计开发;

学习多线程编程,搞明白线程池原理并应用到实际产品中;具备高并发网络通信编程能力,熟练掌握epoll以及libevent的使用和设计;

掌握至少一种数据库编程能力,嵌入式可以学习SQlite;

掌握C/C++编程语言,可以设计linux平台下的应用程序以及后台服务程序,并涉猎其他编程语言,可以学习Python;

修炼内功,学好数学,学习各种编程算法,掌握常用数据结构以及算法的原理和实现,链表、队列、排序、查找等;掌握常用滤波算法及其实现,比如一阶互补滤波、卡尔曼滤波等;掌握PID原理与算法实现;

以上即是嵌入式软件开发的路线,当然不一定适合每个人,但总体来讲掌握这些对以后的进一步发展有很大帮助。